About ACM Research

ACM Research, Inc. (ACM Research) supplies advanced, innovative capital equipment developed for the global semiconductor industry.

The company conducts a substantial majority of its product development, manufacturing, support and services in mainland China through ACM Shanghai. The company performs, through a subsidiary of ACM Shanghai, additional product development and subsystem production in Korea, and the company conducts, through ACM Research, sales and marketing activities focused on sales of ACM Shanghai products in North America, Europe and certain regions in Asia outside mainland China.

Fabricators of advanced integrated circuits, or chips, can use the company's wet-cleaning and other front-end processing tools in numerous steps to improve product yield, even at increasingly advanced process nodes. The company has designed these tools for use in fabricating foundry, logic and memory chips, including dynamic random-access memory, or DRAM, and 3D NAND-flash memory chips. The company also develops, manufactures and sells a range of advanced packaging tools to wafer assembly and packaging customers.

The company has focused its selling efforts on establishing a referenceable base of leading foundry, logic and memory chip makers, whose use of the company's products can influence decisions by other manufacturers. This customer base has helped the company penetrate the mature chip manufacturing markets and build credibility with additional industry leaders. The company has used a 'demo-to-sales' process to place evaluation equipment, or 'first tools,' with a number of selected customers.

As of December 31, 2023, a substantial majority of the company's sales of single-wafer wet-cleaning equipment for front-end manufacturing had been to customers located in Asia, and the company anticipates that a substantial majority of its revenue from these products will continue to come from customers located in this region for the foreseeable future. The company's operation includes sales, marketing and services personnel in North America, Western Europe, and Southeast Asia to expand and support major new customer initiatives for the products of ACM Shanghai to additional regions beyond mainland China.

The company is focused on building a strategic portfolio of intellectual property to support and protect the company's key innovations. The company's tools have been developed using its key proprietary technologies:

Space Alternated Phase Shift, or SAPS, technology for flat and patterned (deep via or deep trench with stronger structure) wafer surfaces. SAPS technology employs alternating phases of megasonic waves to deliver megasonic energy in a highly uniform manner on a microscopic level. The company has shown SAPS technology to be more effective than conventional megasonic and jet spray technologies in removing random defects across an entire wafer, with increasing relative effectiveness at more advanced production nodes.

Timely Energized Bubble Oscillation, or TEBO, technology for patterned wafer surfaces at advanced process nodes. TEBO technology has been developed to provide effective, damage-free cleaning for 2D and 3D patterned wafers with fine feature sizes. The company has demonstrated the damage-free cleaning capabilities of TEBO technology on patterned wafers for feature nodes as small as 1xnm (16 to 19 nanometers, or nm), and the company has shown TEBO technology can be applied in manufacturing processes for patterned chips with 3D architectures having aspect ratios as high as 60-to-1.

Tahoe technology for cost and environmental savings. Tahoe technology delivers high cleaning performance using significantly less sulfuric acid and hydrogen peroxide than is typically consumed by conventional high-temperature single-wafer cleaning tools.

ECP technology for advanced metal plating. The company's Ultra ECP ap, or Advanced Packaging, technology was developed for back-end assembly processes to deliver a more uniform metal layer at the notch area of wafers prior to packaging. The company's Ultra ECP map, or Multi-Anode Partial Plating, technology was developed for front-end wafer fabrication processes to deliver advanced electrochemical copper plating for copper interconnect applications. Ultra ECP map offers improved gap-filling performance for ultra-thin seed layer applications, which is critical for advanced nodes at 28nm, 14nm and beyond.

The company has also introduced and delivered a range of new tools intended to broaden the company's revenue opportunity with global semiconductor manufacturers. Product extensions include the Ultra SFP ap tool for advanced packaging solutions, the Ultra C VI 18-chamber single wafer cleaning tool for advanced memory devices, and the Ultra ECP 3d platform for through-silicon-via, or tsv, application. New product lines include the Ultra fn Furnace, the company's first dry processing tool, and a suite of semi-critical cleaning systems which include single wafer back side cleaning, scrubber, and auto bench cleaning tools.

The company added two major new product categories in 2022 with the launch of the Ultra Pmax PECVD tool, which is equipped with a proprietary designed chamber, gas distribution unit and chuck, and is intended to provide better film uniformity, reduced film stress, and improved particle performance, and the introduction of the Ultra Track tool, a 300mm process tool that delivers uniform air downflow, fast robot handling and customizable software to address specific customer requirements, and has multiple features that enhance performance across defectivity, throughput, and cost of ownership.

The company has been issued more than 498 patents in the United States, the People's Republic of China, or mainland China, Japan, Singapore, Korea and Taiwan.

The company conducts a substantial majority of its product development, manufacturing, support and services in mainland China, with additional product development and subsystem production in Korea. Substantially all of the company's integrated tools are built to order at its manufacturing facilities in the Pudong region of Shanghai, which encompass a total of 236,000 square feet of floor space for production capacity, with leased buildings at the company's Chuansha campus. In May 2020 ACM Shanghai, through its wholly owned subsidiary Shengwei Research (Shanghai), Inc., or ACM Shengwei, entered into an agreement for a land use right in the Lingang region of Shanghai. In 2020, ACM Shengwei began a multi-year construction project for a new 1,000,000 square foot development and production center that will incorporate manufacturing systems and automation technologies and will provide floor space to support significantly increased production capacity and related research and development, or R&D, activities. The company expects to commence initial operations and production activities at the company's Lingang facilities in the first half of 2024 timeframe.

The company's experience has shown that chip manufacturers in mainland China and throughout Asia demand equipment that meets their specific technical requirements and generally prefer to build relationships with local suppliers. The company will continue to seek to leverage its local presence in mainland China and Korea through the company's subsidiaries to address the growing market for semiconductor manufacturing equipment in the region by working closely with regional chip manufacturers to understand their specific requirements, encourage them to adopt the company's technologies, and enable the company to design innovative products and solutions to address their needs.

On November 18, 2021, ACM Shanghai successfully completed its initial public offering of shares of ACM Shanghai in mainland China, which the company refers to as the STAR IPO, and its shares began trading on the Shanghai Stock Exchange's SciTech innovAtion boaRd, known as the STAR Market, which the company refers to as the STAR Listing.

Technology and Product Offerings

Wet Cleaning Equipment for Front End Production Processes

Chip fabricators can use the company's single-wafer wet-cleaning tools in numerous steps to improve product yield in the front-end production process, during which individual devices are patterned in a chip prior to being interconnected on a wafer. The company's wet-cleaning equipment has been developed using the company's proprietary SAPS, TEBO and Tahoe technologies, which allow the company's tools to remove random defects from a wafer surface effectively, without damaging a wafer or its features, even at increasingly advanced process nodes (the minimum line widths on a chip) of 22nm or less. The company use a modular configuration that enables the company to create a wet-cleaning tool meeting the specific requirements of a customer, while using pre-existing designs for chamber, electrical, chemical delivery and other modules. The company's modular approach supports a wide range of customer needs and facilitates the adaptation of the company's model tools for use with the optimal chemicals selected to meet a customer's requirements. The company's tools are offered principally for use in manufacturing chips from 300 millimeter, or mm, silicon wafers, but the company also offer solutions for 150mm and 200mm wafers and for nonstandard substrates, including compound semiconductor, quartz, sapphire, glass and plastics.

SAPS Technology, Applications and Equipment

SAPS Technology

SAPS technology delivers megasonic energy uniformly to every point on an entire wafer by alternating phases of megasonic waves in the gap between a megasonic transducer and the wafer. Radicals for removing random defects are generated in dilute solution, and the radical generation is promoted by megasonic energy. Unlike 'stationary' megasonic transducers used in conventional megasonic cleaning methods, SAPS technology moves or tilts a transducer while a wafer rotates, enabling megasonic energy to be delivered uniformly across all points on the wafer, even if the wafer is warped. The mechanical force of cavitations generated by megasonic energy enhances the mass transfer rate of dislodged random defects and improves particle removal efficiency.

By delivering megasonic energy in a highly uniform manner on a microscopic level, SAPS technology can precisely control the intensity of megasonic energy and can effectively remove random defects of all sizes across the entire wafer in less total cleaning time than conventional megasonic cleaning products, without loss of material or roughing of wafer surfaces. The company has conducted trials demonstrating SAPS technology to be more effective than conventional megasonic and jet spray cleaning technologies as defect sizes shrink from 300nm to 20nm and below. These trials show that SAPS technology has an even greater relative advantage over conventional jet spray technology for cleaning defects between 50 and 65nm in size, and the company expect the relative benefits of SAPS will continue to apply in cleaning even smaller defect sizes.

SAPS Applications

SAPS megasonic cleaning technology can be applied during the chip fabrication process to clean wafer surfaces and interconnects. It also can be used to clean, and lengthen the lifetime, of recycled test wafers.

Wafer Surfaces. SAPS technology can enhance removal of random defects following planarization and deposition, which are among the most important, and most repeated, steps in the fabrication process:

Post CMP: Chemical mechanical planarization, or CMP, uses an abrasive chemical slurry following other fabrication processes, such as deposition and etching, in order to achieve a smooth wafer surface in preparation for subsequent processing steps. SAPS technology can be applied following each CMP process to remove residual random defects deposited or formed during CMP.

Post Hard Mask Deposition: As part of the photolithographical patterning process, a mask is applied with each deposition of a material layer to prevent etching of material intended to be retained. Hard masks have been developed to etch high aspect-ratio features of advanced chips that traditional masks cannot tolerate. SAPS technology can be applied following each deposition step involving hard masks that use nitride, oxide or carbon-based materials to achieve higher etch selectivity and resolution.

For these purposes, SAPS technology uses environmentally friendly dilute chemicals, reducing chemical consumption. Chemical types include dilute solutions of chemicals used in RCA cleaning, such as dilute hydrofluoric acid and RCA SC-1 solutions, and, for higher quality wafer cleaning, functional de-ionized water produced by dissolving hydrogen, nitrogen or carbon dioxide in water containing a small amount of chemicals, such as ammonia. Functional water removes random defects by generating radicals, and megasonic excitation can be used in conjunction with functional water to further increase the generation of radicals. Functional water has a lower cost and environmental impact than RCA solutions, and using functional water is more efficient in eliminating random defects than using dilute chemicals or de-ionized water alone. The company has shown that SAPS megasonic technology using functional water exhibits high efficiency in removing random defects, especially particles smaller than 65nm, with minimal damage to structures.

Interconnects and Barrier Metals. Each successive advanced process node has led to finer feature sizes of interconnects such as contacts, which form electrical pathways between a transistor and the first metal layer, and vias, which form electrical pathways between two metal layers. Advanced nodes have also resulted in higher aspect ratios for interconnect structures, with thinner, redesigned metal barriers being used to prevent diffusion. SAPS technology can improve the removal of residues and other random defects from interconnects during the chip fabrication process:

Post Contact/Via Etch: Wet etching processes are commonly used to create patterns of high-density contacts and vias. SAPS technology can be applied after each such etching process to remove random defects that could otherwise lead to electrical shorts.

Pre Barrier-Metal Deposition: Copper wiring requires metal diffusion barriers at the top of via holes to prevent electrical leakage. SAPS technology can be applied prior to deposition of barrier metal to remove residual oxidized copper, which otherwise would adhere poorly to the barrier and impair performance.

For these applications, SAPS technology uses environmentally friendly dilute chemicals such as dilute hydrofluoric acid, RCA SC-1 solution, ozonated de-ionized water and functional de-ionized water with dissolved hydrogen. These chemical solutions take the place of piranha solution, a high-temperature mixture of sulfuric acid and hydrogen peroxide used by conventional wet wafer cleaning processes. The company has shown that SAPS technology exhibits greater efficiency in removing random defects, and lower levels of material loss, than conventional processes, and the company's chemical solutions are less expensive and more environmentally conscious than piranha solution.

Recycled Test Wafers. In addition to using silicon wafers for chip production, chip manufacturers routinely process wafers through a limited portion of the front-end fabrication steps in order to evaluate the health, performance and reliability of those steps. Manufacturers also use wafers for non-product purposes such as inline monitoring. Wafers used for purposes other than manufacturing revenue products are known as test wafers, and it is typical for twenty to thirty percent of the wafers circulating in a fab to be test wafers. In light of the significant cost of wafers, manufacturers seek to re-use a test wafer for more than one test. As test wafers are recycled, surface roughness and other defects progressively impair the ability of a wafer to complete tests accurately. SAPS technology can be applied to reduce random defect levels of a recycled wafer, enabling the test wafer to be reclaimed for use in additional testing processes. For these purposes, SAPS technology includes improved fan filter units that balances intake and exhaust flows, precise temperature and concentration controls that ensure better handling of concentrated acid processes, and two-chemical recycle capability that reduces chemical consumption.

SAPS Equipment

The company offers two principal models of wet wafer cleaning equipment based on the company's SAPS technology, Ultra C SAPS II and Ultra C SAPS V. Each of these models is a single-wafer, serial-processing tool that can be configured to customer specifications and, in conjunction with appropriate dilute chemicals, used to remove random defects from wafer surfaces or interconnects and barrier metals as part of the chip front-end fabrication process or for recycling test wafers. By combining the company's megasonic and chemical cleaning technologies, the company has designed these tools to remove random defects with greater efficacy and efficiency than conventional wafer cleaning processes, with enhanced process flexibility and reduced quantities of chemicals. Each of the company's SAPS models was initially built to meet specific requirements of a key customer.

SAPS II (released in 2011). Highlights of the company's SAPS II equipment include compact design, with footprint of 2.65m x 4.10m x 2.85m (WxDxH), requiring limited clean room floor space; up to 8 chambers, providing throughput of up to 225 wafers per hour; double-sided cleaning capability, with up to 5 cleaning chemicals for process flexibility; 2-chemical recycling capability for reduced chemical consumption; image wafer detection method for lowering wafer breakage rates; and chemical delivery module for delivery of dilute hydrofluoric acid, RCA SC-1 solution, functional de-ionized water and carbon dioxide to each of the chambers.

SAPS V (released in 2014). SAPS V includes SAPS II features with the following upgrades: compact design, with footprint of 2.55m x 5.1m x 2.85m (WxDxH), requiring limited clean room floor space; up to 12 chambers, providing throughput of up to 375 wafers per hour; chemical supply system integrated into mainframe; inline mixing method replaces tank auto changing, reducing process time; and improved drying technology using hot isopropyl alcohol and de-ionized water.

TEBO Technology, Applications and Equipment

TEBO Technology

The company developed TEBO technology for application in wet wafer cleaning during the fabrication of 2D and 3D wafers with fine feature sizes. TEBO technology facilitates effective cleaning even with patterned features too small or fragile to be addressed by conventional jet spray and megasonic cleaning technologies.

TEBO technology solves the problems created by transient cavitation in conventional megasonic cleaning processes. Cavitation is the formation of bubbles in a liquid, and transient cavitation is a process in which a bubble in fluid implodes or collapses. In conventional megasonic cleaning processes, megasonic energy forms bubbles and then causes those bubbles to implode or collapse, blasting destructive high-pressure, high-temperature micro jets toward the wafer surface. The company's internal testing has confirmed that at any level of megasonic energy capable of removing random defects, the sonic energy and mechanical force generated by transient cavitation are sufficiently strong to damage fragile patterned structures with features less than 70nm.

TEBO technology provides multi-parameter control of cavitation by using a sequence of rapid changes in pressure to force a bubble in liquid to oscillate at controlled sizes, shapes and temperatures, rather than implode or collapse. As a result, cavitation remains stable during TEBO megasonic cleaning processes, and a chip fabricator can, using TEBO technology, apply the level of megasonic energy needed to remove random defects without incurring the pattern damage created by transient cavitation in conventional megasonic cleaning.

The company has demonstrated the damage-free or low-damage cleaning capabilities of TEBO technology on customers' patterned wafers as small as 1xnm (16nm to 19nm), and TEBO technology will be applicable in even smaller fabrication process nodes. TEBO technology can be applied in manufacturing processes for conventional 2D chips with fine features and advanced chips with 3D structures, including Fin Field Effect Transistors or FinFET, DRAM, 3D NAND and 3D cross point memory, and the company expects it will be applicable to other 3D architectures developed in the future, such as carbon nanotubes and quantum devices. As a result of the thorough, controlled nature of TEBO processes, cleaning time for TEBO-based solutions may take longer than conventional megasonic cleaning processes. Conventional processes have proven ineffective, however, for process nodes of 20nm or less, and the increased yield that can be achieved by using TEBO technology for nodes up to 70nm can more than offset the cost of the additional time in utilizing TEBO technology.

TEBO Applications

At process nodes of 28nm and less, chip makers face escalating challenges in eliminating nanometric particles and maintaining the condition of inside pattern surfaces. In order to maintain chip quality and avoid yield loss, cleaning technologies must control random defects of diminishing killer defect sizes, without roughing or otherwise damaging surfaces of transistors, interconnects or other wafer features. TEBO technology can be applied in numerous steps throughout the manufacturing process flow for effective, damage-free cleaning:

Memory Chips: The company estimates that TEBO technology can be applied in as many as 50 steps in the fabrication of a DRAM chip, consisting of up to 10 steps in cleaning ISO structures, 20 steps in cleaning buried gates, and 20 steps in cleaning high aspect-ratio storage nodes and stacked films.

Logic Chips: In the fabrication process for a logic chip with a FinFET structure, the company estimates that TEBO technology can be used in 15 or more cleaning steps.

For purposes of solving inside pattern surface conditions for memory or logic chips, TEBO technology uses environmentally friendly dilute chemicals such as RCA SC-1 and hydrogen gas doped functional water.

TEBO Equipment

The company offers two models of wet wafer cleaning equipment based on the company's TEBO technology, Ultra C TEBO II and Ultra C TEBO V. Each of these models is a single-wafer, serial-processing tool that can be configured to customer specifications and, in conjunction with appropriate dilute chemicals, used at numerous manufacturing processing steps for effective, damage-free cleaning of chips at process nodes of 28nm or less. TEBO equipment solves the problem of pattern damage caused by transient cavitation in conventional jet spray and megasonic cleaning processes, providing better particle removal efficiency with limited material loss or roughing. TEBO equipment is being evaluated by a select group of leading memory and logic chip customers.

Each model of TEBO equipment includes an equipment front-end module, or EFEM, which moves wafers from chamber to chamber; one or more chamber modules, each equipped with a TEBO megasonic generator system; an electrical module to provide power for the tool; and a chemical delivery module.

Ultra C TEBO II (released in 2016). Highlights of the company's Ultra C TEBO II equipment include compact design, with footprint of 2.25m x 2.25m x 2.85m (WxDxH); up to 8 chambers with an upgraded transport system and optimized robotic scheduler, providing throughput of up to 300 wafers per hour; EFEM module consisting of 4 load ports, transfer robot and 1 process robot; and focus on dilute chemicals contributes to environmental sustainability and lower cost of ownership.

Ultra C TEBO V (released in 2016). Highlights of the company's Ultra C TEBO V equipment include footprint of 2.45m x 5.30m x 2.85m (WxDxH); up to 12 chamber modules, providing throughput of up to 300 wafers per hour; EFEM module consisting of 4 load ports, 1 transfer robot and 1 process robot; and chemical delivery module for delivery of isopropyl alcohol, dilute hydrofluoric acid, RCA SC-1 solution, functional de-ionized water and carbon dioxide to each of the chambers.

Tahoe Overview

The company's Ultra-C Tahoe wafer cleaning tool can deliver high cleaning performance using significantly less sulfuric acid and hydrogen peroxide than is typically consumed by conventional high-temperature single-wafer cleaning tools. During normal single-wafer cleaning processes, only a fraction of the acid reacts with the wafer surface, while the majority is wasted as acid spins off the wafer and requires significant cost and effort to be recycled. Tahoe employs a proprietary hybrid approach in which the sulfuric acid cleaning steps are processed in batch mode, and the final stage cleaning are processed with single-wafer cleaning technologies. In addition to providing cost savings resulting from vastly reduced sulfuric acid consumption, Ultra-C Tahoe meets the needs of customers who face increased environmental regulations and demand new, more environmentally friendly tools. The company delivered the company's first Ultra C Tahoe tool to a strategic customer in 2019.

Advanced Packaging and other Back-End Processing Tools

The company leverages its technology and expertise to provide a range of single-wafer tools for back-end wafer assembly and packaging factories. The company develops, manufactures and sells a wide range of advanced packaging tools, such as coaters, developers, photoresist strippers, scrubbers, wet etchers and copper-plating tools. The company focuses on providing custom-made, differentiated equipment that incorporates customer-requested features at a competitive price.

For example, the company's Ultra C Coater is used in applying photoresist, a light-sensitive material used in photolithography to transfer a pattern from a mask onto a wafer. Coaters typically provide input and output elevators, shuttle systems and other devices to handle and transport wafers during the coating process. Unlike most coaters, the Ultra C Coater is fully automated. Based on requests from customers, the company developed and incorporated the special function of chamber auto-clean module into the Ultra C Coater, which further differentiates it from other products in the market by reducing or eliminating the cleaning of shroud in the coater which increases the tool's continuous production time. The Ultra C Coater is designed to deliver improved throughput and more efficient tool utilization while eliminating particle generation.

The company's other advanced packaging tools include: Ultra ECP ap, which delivers a uniform metal layer to finished wafers prior to packaging; Ultra C Developer, which applies liquid developer to selected parts of photoresist to resolve an image; Ultra C PR Megasonic-Assisted Stripper, which removes photoresist; Ultra C Scrubber, which scrubs and cleans wafers; Ultra C Thin Wafer Scrubber, which addresses a sub-market of cleaning very thin wafers for certain Asian assembly factories; and Ultra C Wet Etcher, which etches silicon wafers and copper and titanium interconnects.

Customers

Since 2009, the company has delivered more than 765 tools to its customers, more than 650 of which were repeat orders or acceptances upon contractual performance obligations having been met and thereby generated revenue to the company. As of December 31, 2023, substantially all of the company's sales of equipment for semiconductor-manufacturing had been to customers located in Asia, and the company anticipates that a substantial majority of the company's revenue from these products will continue to come from customers located in this region for the foreseeable future. The company has begun to add to its efforts to further address customers in North America, Western Europe and Southeast Asia, by expanding the company's direct sales teams and increasing its global marketing activities.

The company's front-end customers have included: Shanghai Huali Microelectronics Corporation, together with Huahong Semiconductor Ltd., collectively known as The Shanghai Huahong (Group) Company, Ltd., or The Huali Huahong Group, a leading mainland China-based foundry; Semiconductor Manufacturing International Corporation, or SMIC, a leading mainland China-based foundry; SK Hynix Inc., a leading Korean memory chip company; Yangtze Memory Technologies Co., Ltd., or YMTC, a leading mainland China-based memory chip company, together with one of its subsidiaries; ChangXin Memory Technologies, or CXMT, a leading mainland China-based memory chip company; and SiEn, a leading mainland China-based power-semiconductor chip company. The company's wafer assembly and packaging customers have included: Jiangyin Changdian Advanced Packaging Co. Ltd., a mainland China-based wafer bumping packaging house that is a subsidiary of JCET Group Co., Ltd.; Nantong Tongfu Microelectronics Co., Ltd., a mainland China-based chip assembly and testing company that is a subsidiary of Nantong Fujitsu Microelectronics Co., Ltd.; Nepes Co., Ltd., a semiconductor packaging company based in Korea; and Wafer Works Corporation, a mainland China-based wafer supplier.

In 2023, 45.5% of the company's revenue was derived from three customers: SMIC accounted for 16.7% of the company's revenue; SiEn accounted for 15.4% of the company's revenue; and CXMT; accounted for 13.4% of the company's revenue.

Sales and Marketing

The company markets and sells its products worldwide using a combination of its direct sales force and third-party representatives. The company employs direct sales teams in mainland China, the United States, Southeast Asia, and Europe. The company also employs field application engineers, who are typically co-located with the company's direct sales teams, to provide technical pre- and post-sale support and other assistance to existing and potential customers throughout the customers' fab planning and production line qualification and fab expansion phases. The company's field application engineers are organized by end markets, as well as core competencies in hardware, control system, software and process development to support the company's customers.

To supplement the company's direct sales teams, the company has contacts with several independent sales representatives in mainland China, Korea and Taiwan. The company selects these independent representatives based on their ability to provide effective field sales, marketing forecast and technical requirement updates for the company's products. In the case of representatives, the company's customers place purchase orders with the company directly rather than with the representatives.

Research and Development

The company's research and development expense totaled $92.7 million in 2023.

Intellectual Property

As of December 31, 2023, the company had 64 issued patents, and 29 patents pending, in the United States. These patents carry expiration dates from 2027 through 2038. Many of the U.S. patents and applications have also been filed internationally, including one or more of the European Union, Japan, mainland China, Singapore, Korea, and Taiwan. Specifically, the company owns patents in wafer cleaning, electro-polishing and plating, wafer preparation, and other semiconductor processing technologies. The company has been issued more than 498 patents in the United States, mainland China, Japan, Korea, Singapore and Taiwan.

The company manufactures advanced single-wafer cleaning systems equipped with the company's SAPS, TEBO and Tahoe technologies. The company has 57 patents granted internationally protecting the company's SAPS technologies. The company has filed 11 international patent applications for key TEBO technologies, and 5 for Tahoe, in accordance with the Patent Cooperation Treaty. In addition the company has patented technologies for SFP and ECP that are embedded in certain tools. The company also has patented technologies in other semiconductor processing areas, including wafer preparation and several specific processing steps.

Competition

Key competitors for the company's newly-introduced PECVD and Track products include Lam Research Corporation, Applied Materials, Inc., KINGSEMI Co., Ltd. and Suzhou Jingtuo Semiconductor Technology Co., Ltd.

History

ACM Research, Inc. was founded in 1998. The company was incorporated in California in 1998 and redomesticated in Delaware in 2016.

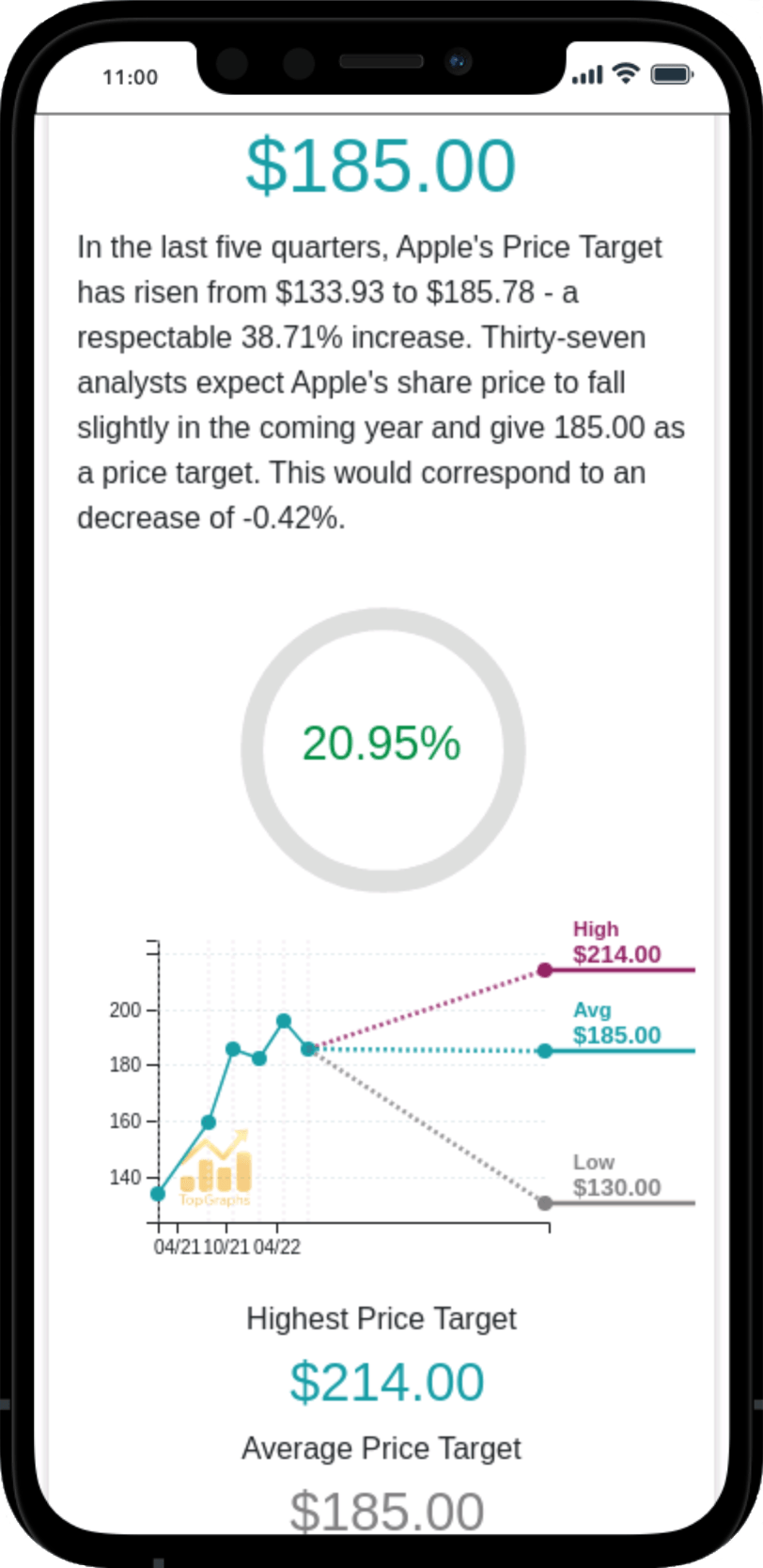

Stock Value

Stock Value